File:PCI-host-controller-in-x86-architecture.png

From OSDev Wiki

Full resolution (562 × 894 pixels, file size: 20 KB, MIME type: image/png)

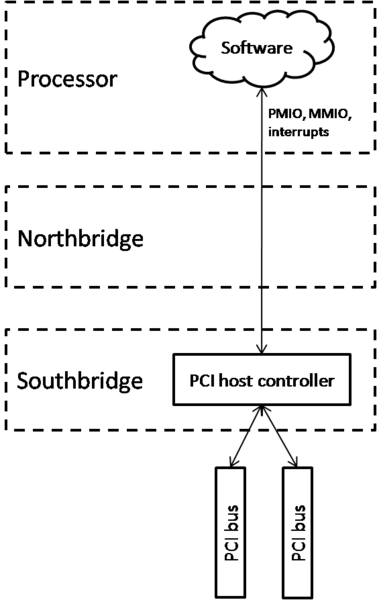

In the x86 architecture, the PCI host controller is integrated into the Southbridge. The Processor/Northbridge/Southbridge, produced by a single vendor, exposes the PCI host controller (and, by extension, the PCI buses) to software via port-mapped IO, memory-mapped IO, and interrupts.

File history

Click on a date/time to view the file as it appeared at that time.

| Date/Time | Thumbnail | Dimensions | User | Comment | |

|---|---|---|---|---|---|

| current | 15:34, 20 February 2013 |  | 562 × 894 (20 KB) | Intx13 (Talk | contribs) | (In the x86 architecture, the PCI host controller is integrated into the Southbridge. The Processor/Northbridge/Southbridge, produced by a single vendor, exposes the PCI host controller (and, by extension, the PCI buses) to software via port-mapped IO, mem) |

- Edit this file using an external application (See the setup instructions for more information)

File usage

The following page links to this file: