MADT

| ACPI |

|---|

| Fixed Tables |

| Differentiated Tables |

| Tools/Libs |

The Multiple APIC Description Table (MADT) is an ACPI table which provides informations necessary for operation on systems with APIC, SAPIC, GIC, or LPIC implementations. As of June 17th, 2023, its latest definition is provided in the ACPI Specification Version 6.5, section 5.2.12. Multiple APIC Description Table (MADT).

Introduction

The MADT describes all of the interrupt controllers in the system. It can be used to enumerate the processors currently available.

You can look at the length field in the MADT's header to determine when you have read all the entries.

Table Structure

The MADT starts with the standard ACPI table header. The signature is 'APIC'.

| Offset (hex) | Length | Description |

|---|---|---|

| 00 | 4 | Signature 'APIC' |

| 04 | 4 | Length |

| 08 | 1 | Revision |

| 09 | 1 | Checksum |

| 0a | 6 | OEMID |

| 10 | 8 | OEM Table ID |

| 18 | 4 | OEM Revision |

| 1c | 4 | Creator ID |

| 20 | 4 | Creator Revision |

After the standard header, the following fields are located.

| Offset (hex) | Length | Description |

|---|---|---|

| 24 | 4 | Local APIC Address |

| 28 | 4 | Flags (1 = Dual 8259 Legacy PICs Installed) |

If bit 0 in the flags field is set then you need to mask all the 8259 PIC's interrupts, but you should probably do this anyway.

After the Flags field, starting at offset 0x2C, the rest of the MADT table contains a sequence of variable length records which enumerate the interrupt devices on this machine. Each record begins with the following header fields.

| Offset (hex) | Length | Description |

|---|---|---|

| 0 | 1 | Entry Type |

| 1 | 1 | Record Length |

Based on the Entry Type field value, the rest of the record layout can be determined.

Entry Type 0: Processor Local APIC

This type represents a single logical processor and its local interrupt controller.

| Offset (hex) | Length | Description |

|---|---|---|

| 2 | 1 | ACPI Processor ID |

| 3 | 1 | APIC ID |

| 4 | 4 | Flags (bit 0 = Processor Enabled) (bit 1 = Online Capable) |

If flags bit 0 is set the CPU is able to be enabled, if it is not set you need to check bit 1. If that one is set you can still enable it, if it is not the CPU can not be enabled and the OS should not try.

Entry Type 1: I/O APIC

This type represents a I/O APIC. The global system interrupt base is the first interrupt number that this I/O APIC handles. You can see how many interrupts it handles using the register by getting the number of redirection entries from register 0x01, as described in IO APIC Registers.

| Offset (hex) | Length | Description |

|---|---|---|

| 2 | 1 | I/O APIC's ID |

| 3 | 1 | Reserved (0) |

| 4 | 4 | I/O APIC Address |

| 8 | 4 | Global System Interrupt Base |

Entry Type 2: I/O APIC Interrupt Source Override

This entry type contains the data for an Interrupt Source Override. This explains how IRQ sources are mapped to global system interrupts. For example, IRQ source for the timer is 0, and the global system interrupt will usually be 2. So you could look for the I/O APIC with the base below 2 and within its redirection entries, then make the redirection entry for (2 - base) to be the timer interrupt.

| Offset (hex) | Length | Description |

|---|---|---|

| 2 | 1 | Bus Source |

| 3 | 1 | IRQ Source |

| 4 | 4 | Global System Interrupt |

| 8 | 2 | Flags (see below) |

Entry type 3: I/O APIC Non-maskable interrupt source

Specifies which I/O APIC interrupt inputs should be enabled as non-maskable.

| Offset (hex) | Length | Description |

|---|---|---|

| 2 | 1 | NMI Source |

| 3 | 1 | Reserved |

| 4 | 2 | Flags (see below) |

| 6 | 4 | Global System Interrupt |

Entry Type 4: Local APIC Non-maskable interrupts

Configure these with the LINT0 and LINT1 entries in the Local vector table of the relevant processor(')s(') local APIC.

| Offset (hex) | Length | Description |

|---|---|---|

| 2 | 1 | ACPI Processor ID (0xFF means all processors) |

| 3 | 2 | Flags (see below) |

| 5 | 1 | LINT# (0 or 1) |

Entry Type 5: Local APIC Address Override

Provides 64 bit systems with an override of the physical address of the Local APIC. There can only be one of these defined in the MADT. If this structure is defined, the 64-bit Local APIC address stored within it should be used instead of the 32-bit Local APIC address stored in the MADT header.

| Offset (hex) | Length | Description |

|---|---|---|

| 2 | 2 | Reserved |

| 4 | 8 | 64-bit physical address of Local APIC |

Entry Type 9: Processor Local x2APIC

Represents a physical processor and its Local x2APIC. Identical to Local APIC; used only when that struct would not be able to hold the required values.

| Offset (hex) | Length | Description |

|---|---|---|

| 2 | 2 | Reserved |

| 4 | 4 | Processor's local x2APIC ID |

| 8 | 4 | Flags (same as the Local APIC flags) |

| C | 4 | ACPI ID |

Flags

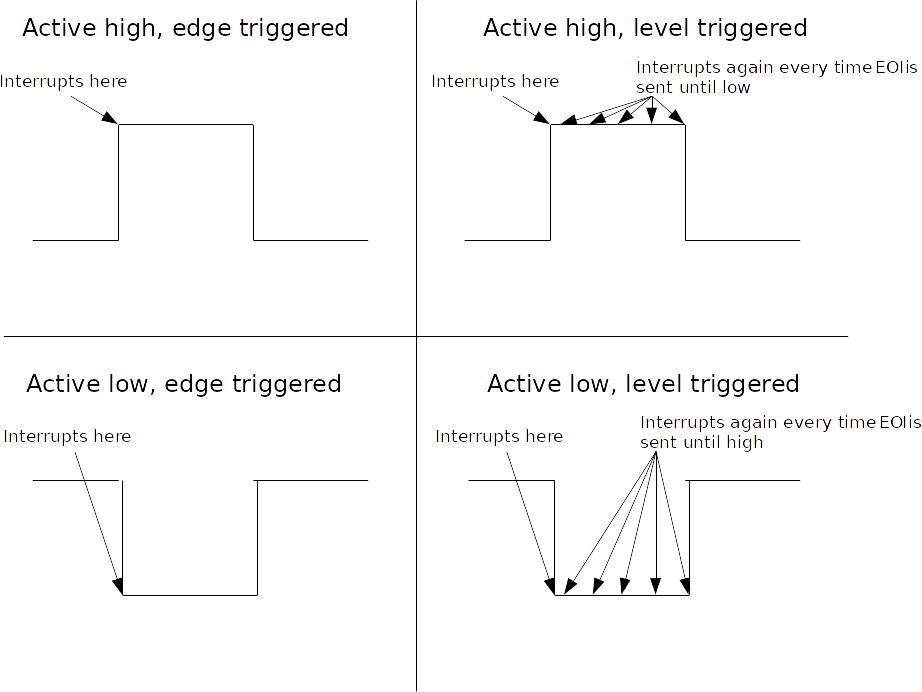

Entry type 2, 3 and 4 have a flags field, which is useful for settings up the I/O APIC redirection entry or local vector table entry respectively. If (flags & 2) then the interrupt is active when low, and if (flags & 8) then interrupt is level-triggered.

Here is a diagram of the interrupt types: