Uploads by Intx13

Jump to navigation

Jump to search

This special page shows all uploaded files.

| Date | Name | Thumbnail | Size | Description | Versions |

|---|---|---|---|---|---|

| 16:53, 11 November 2015 | OVMF run app.png (file) |  |

34 KB | 1 | |

| 15:45, 11 November 2015 | OVMF browse fs.png (file) |  |

33 KB | 1 | |

| 14:32, 11 November 2015 | OVMF shell.png (file) |  |

17 KB | 1 | |

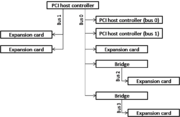

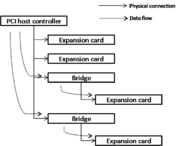

| 21:15, 20 February 2013 | Multi-bus-PCI-host-controller-with-multiple-bridges.png (file) |  |

17 KB | This figure illustrates a system with a PCI host controller that supports two buses, one of which has two bridges. To ensure that the two bridged expansion cards are accessible, a daisy-chain would need to be set up from the PCI host controller (either it | 1 |

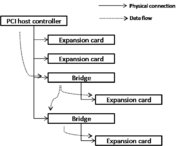

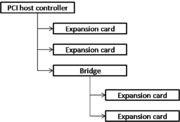

| 21:04, 20 February 2013 | Correct-flow-of-PCI-traffic.png (file) |  |

16 KB | This figure illustrates how traffic really flows from the host controller to bridges and the devices they host. Bridges are daisy-chained until there is a single path from the host controller through every bridge. | 1 |

| 21:00, 20 February 2013 | Incorrect-flow-of-PCI-traffic.png (file) |  |

17 KB | Sadly this is NOT how traffic flows from a PCI host controller to devices connected to bridges. However, it simplifies things to start with this figure when introducing bridges. | 1 |

| 20:48, 20 February 2013 | PCI-host-controller-and-single-bridge.png (file) |  |

9 KB | In this illustration, a PCI host controller has three attached devices. One of those devices is a bridge, which has two attached devices. Traffic destined for one of the devices attached to the bridge flows from the host controller to the bridge and then | 1 |

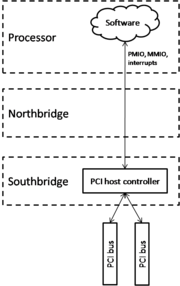

| 20:34, 20 February 2013 | PCI-host-controller-in-x86-architecture.png (file) |  |

20 KB | In the x86 architecture, the PCI host controller is integrated into the Southbridge. The Processor/Northbridge/Southbridge, produced by a single vendor, exposes the PCI host controller (and, by extension, the PCI buses) to software via port-mapped IO, mem | 1 |

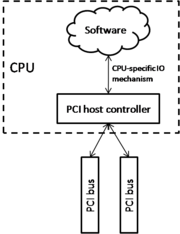

| 20:28, 20 February 2013 | PCI-host-controller-as-software-interface.png (file) |  |

14 KB | In modern systems the PCI host controller is often integrated into the CPU and exposes PCI buses to software via some CPU-specific IO mechanism, such as memory-mapped IO. This is in contrast with USB, where the USB host controller is connected to the CPU | 1 |

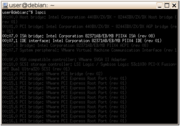

| 20:06, 20 February 2013 | Lspci-with-multifunction-device-highlighted.png (file) |  |

65 KB | This is the output of the "lspci" command on a Debian installation. The highlighted entries illustrate a multi-function PCI device that uses functions 0 and 1 on bus 0, slot 7. | 1 |