User:Foliagecanine/Paging in Long Mode

Paging in Long Mode is very similar to paging in protected mode. It is based off of Physical Address Extension.

Paging Structures

Page-map Level 4 Tables and Entries

PML4 Tables, or Page-map Level 4 Tables, are the topmost paging structure. It is an array of 512 PML4Es (Page-map Level 4 Entries).

Each PML4E points to a PDPT (Page Directory Pointer Table). PML4Es are 64 bits in length and use the following format:

| Bit(s) | Name | Description |

|---|---|---|

| 0 | P | Page Present |

| 1 | R/W | Read/write (0=read only) |

| 2 | U/S | User/supervisor (0=supervisor only) |

| 3 | PWT | Page write-through |

| 4 | PCD | Page cache disable |

| 5 | A | Accessed |

| 6 | IGN | Ignore |

| 8:7 | MBZ | Must Be Zero |

| 11:9 | AVL | Available to Software |

| 51:12 | Page Directory Pointer Base Address | First 36 bits of the pointer to a page containing a Page Directory Pointer Table |

| 62:52 | Available | Available |

| 63 | NX | No-execute/disable execution |

PML4 Tables must be 4KiB aligned due to the fact that the addresses use 36 bits, but can address up to 48 bits.

Page Directory Pointer Tables and Entries

PDPTs, or Page Directory Pointer Tables, are arrays of 512 Page Directory Pointer Entries. PDPTs are the level below PML4Ts but above PDs.

Each PDPTE is 64 bits in length and use the following format:

| Bit(s) | Name | Description |

|---|---|---|

| 0 | P | Page Present |

| 1 | R/W | Read/write (0=read only) |

| 2 | U/S | User/supervisor (0=supervisor only) |

| 3 | PWT | Page write-through |

| 4 | PCD | Page cache disable |

| 5 | A | Accessed |

| 6 | IGN | Ignore |

| 7 | PS | Size (0 = <1GiB, 1 = 1GiB pages) |

| 8 | IGN | Ignore |

| 11:9 | AVL | Available to Software |

| 51:12 | Page Directory Base Address | First 36 bits of the pointer to a page containing a Page Directory.

Will point to a 1GiB page if PS=1 and is supported. |

| 62:52 | Available | Available |

| 63 | NX | No-execute/disable execution |

The S bit is dependent on whether 1GiB pages are supported. For more information on 1GiB pages, see the AMD64 Architecture Programmer's Manual section 5.3.5.

PDPTs must be 4KiB aligned.

Page Directories and Page Directory Entries

PDs, or Page Directories, are arrays of 512 Page Directory Entries. PDs are the level below PDPTs but above PTs.

Each Page Directory Entry is 64 bits long and uses the following format:

| Bit(s) | Name | Description |

|---|---|---|

| 0 | P | Page Present |

| 1 | R/W | Read/write (0=read only) |

| 2 | U/S | User/supervisor (0=supervisor only) |

| 3 | PWT | Page write-through |

| 4 | PCD | Page cache disable |

| 5 | A | Accessed |

| 6 | IGN | Ignore |

| 7 | PS | Size (0 = <2MiB, 1 = 2MiB pages) |

| 8 | IGN | Ignore |

| 11:9 | AVL | Available to Software |

| 51:12 | Page Table Base Address | First 36 bits of the pointer to a page containing Page Table

Will point to a 2MiB page if PS=1. |

| 62:52 | Available | Available |

| 63 | NX | No-execute/disable execution |

PDs must be 4KiB aligned.

Page Tables and Entries

The lowest level of tables are Page Tables. They are arrays of 512 PTEs (Page Table Entries). Page Table Entries point to 4KiB pages.

Each Page Table Entry is 64 bits long and uses the following format:

| Bit(s) | Name | Description |

|---|---|---|

| 0 | P | Page Present |

| 1 | R/W | Read/write (0=read only) |

| 2 | U/S | User/supervisor (0=supervisor only) |

| 3 | PWT | Page write-through |

| 4 | PCD | Page cache disable |

| 5 | A | Accessed |

| 6 | D | Dirty |

| 7 | PAT | (Ignore) |

| 8 | G | Global Translation |

| 11:9 | AVL | Available to Software |

| 51:12 | Physical Page Base Address | First 36 bits of the pointer to a physical page of memory

Will point to a 2MiB page if PS=1. |

| 62:52 | Available | Available |

| 63 | NX | No-execute/disable execution |

CR3

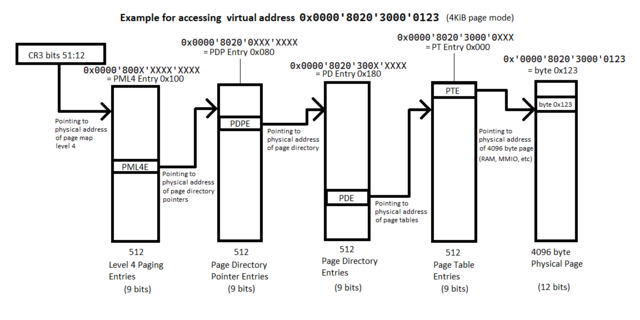

Bits 51:12 of the CR3 register will point to a PML4T.

Determining Physical Addresses

To determine a physical address from a virtual address, the following is used:

- The PML4T index is determined by bits 47:39 of the virtual address.

- If the P bit is set, The PML4E will point to a PDPT.

- The PDPT index is determined by bits 38:30 of the virtual address.

- If the P and S bits are set (and 1GiB pages are supported), the PDPE will point to a 1GiB page. Otherwise, if the P bit is set, it will point to a PD.

- The PD index is determined by bits 29:21 of the virtual address.

- If the P and S bits are set, the PDE will point to a 2MiB page. Otherwise, if the P bit is set, it will point to a PT.

- The PT index is determined by biys 20:12 of the virtual address.

- If the P bit is set, the PTE will point to a 4KiB page.

- Any remaining bits are ORed with the physical address to determine the final virtual address

- If at any step the P bit is not set, it will produce a #PF (see Exceptions#Page_Fault).

- If at any step the R/W bit is not set and the operation is a write, it will produce a #PF.

- If at any step the U/S bit is not set and the proccessor is not in Ring 0, it will produce a #PF.

- If at any step reserved (MBZ) bits are set to 1, it will produce a #PF.

- If at any step the NX bit is set and the operation is an instruction fetch, it will produce a #PF.