User:Gravaera/ARM AMBA Advanced Peripheral Bus

This page seeks to provide a quick refresher reference on the ARM AMBA (Advanced Microcontroller Bus Architecture's) APB (Advanced Peripheral Bus). This is a low-power bus, meant to host low performance microcontrollers, but be able to also interface with the higher powered AHB-Lite (Advanced High-performance Bus) and the AXI (Advanced eXtensible Interface). APB is optimized for low power consumption and reduced interface complexity.

At the time of writing, this page is current with AMBA APB version 3.

Logical description

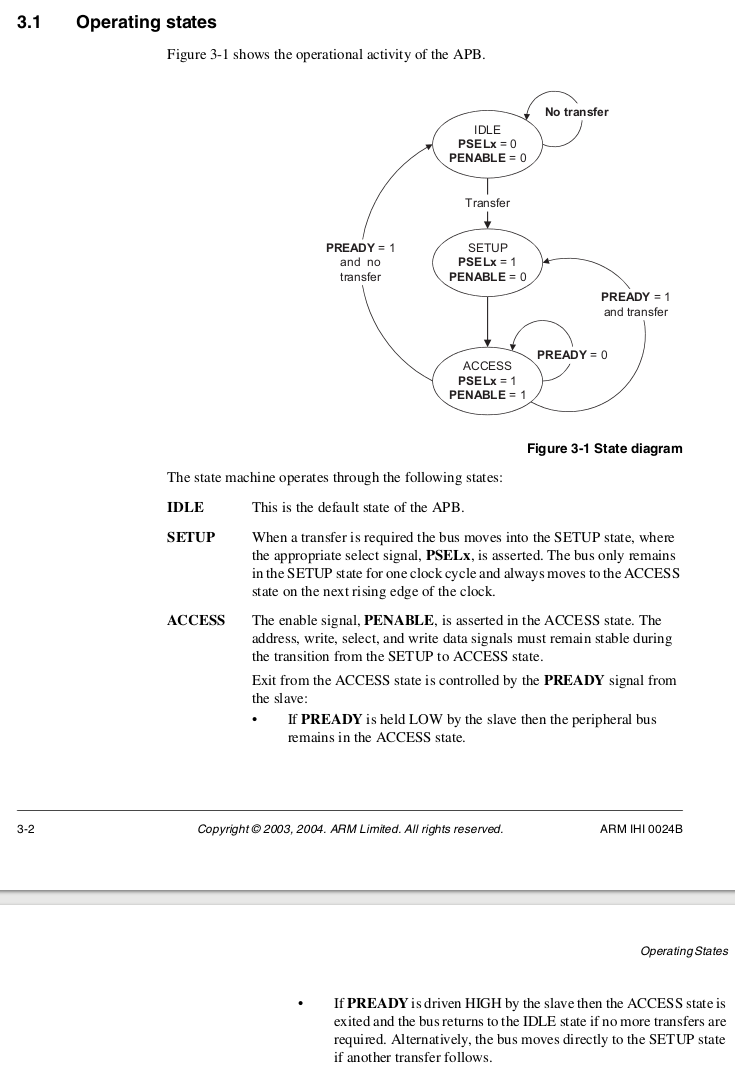

- The APB transitions lines from HIGH/LOW or LOW/HIGH on the HIGH phase of the clock.

- Each transfer takes at least 2 cycles.

- APB uses an unpipelined logical protocol.

Physical layer description

APB has a total of 7 lines.

- PCLK:

- PADDR:

- PWRITE:

- PSEL:

- PENABLE:

- PWDATA:

- PREADY:

APB version 3 adds the PSLVERR line to indicate an error condition during transfer.

- PSLVERR: As of APBv3. It is recommended (not required) that PSLVERR be driven low while it is not being sampled. PSLVERR can be asserted for both read and write transactions. PSLVERR is only sampled on the last cycle of an APB transfer. Failed transactions may or may not have altered the state of the peripheral. This is peripheral specific. PSLVERR does not mean that a write transaction has not updated the peripheral. PSLVERR means that read transactions may return invalid data; in particular, there is no requirement for failed transactions indicated by PSLVERR to return all 0s from a read.

Protocol description

APB slaves can extend APB transfers by using the PREADY signal. The slave does this by driving PREADY low during the ACCESS phase when PENABLE is high. As a result of PREADY being held low by the slave, the PADDR, PWRITE, PSEL and PENABLE signals remain unchanged for the additional (extended) cycles during which PREADY is held low. When the transfer is done, the slave drives PREADY high. This transfer extension facility therefore is not for pausing/controlling the master's transfer rate, but for indicating when a transfer is over.

State diagram:

Signals

A write transaction is indicated by PWRITE being held HIGH. A read transaction is indicated by PWRITE being held LOW.

Mapping to AHB

PSLVERR is mapped to the HRESP=ERROR AHB signal state for both read and write transactions on the AHB. This is achieved by directly mapping APB's PSLVERR to AHB's HRESP[0].

Mapping to AXI

PSLVERR is mapped to RRESP/BRESP=SLVERR AHB signal state. This is achieved by mapping the PSLVERR to RRESP[1] for reads and to BRESP[1] for writes.